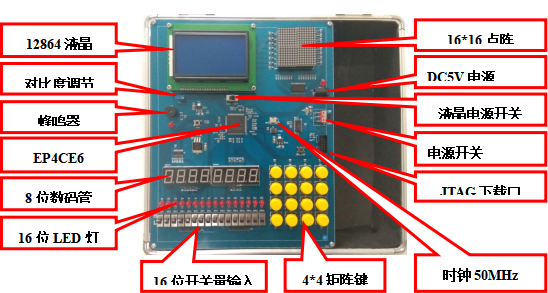

EDA/FPGA实验箱(ALTERA入门款)

基于ALTERA 的FPGA/EDA实验箱,基础入门版,欢迎联系合作!

EP4CE6E144C8N,封装:LQFP144,逻辑单元:6272 LEs ,内存270Kbit,乘法器:15个,全局锁相环:2个,时钟单元:10个,最大IO:179;

产品服务

-

提交需求

-

策划设计

-

技术开发

-

维护修改

-

售后服务

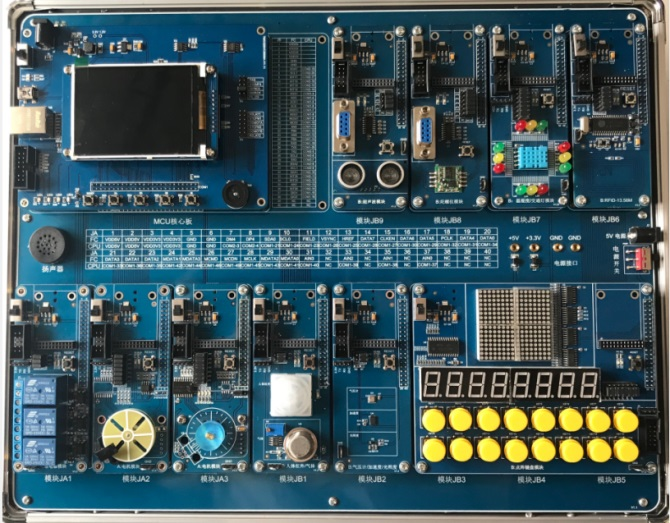

EDA/FPGA实验箱是一款FPGA教学实验系统,满足《EDA技术与应用》、《FPGA原理与应用技术》、《SOPC技术应用》的基础教学而设计开发,该系统基于ALTERA的EP4CE30,实现了多模块的应用实验。它是集学习、应用编程、开发研究于一体多功能创新平台。在实验板上有丰富的外围扩展资源。

配套实验项目

第1章 EP4CE6实验系统的资源介绍

1、 系统功能概述

2、 各部分功能对应管脚

第2章 开发环境安装与使用说明

1、 Quartus II工具介绍

2、 安装Quartus II环境

3、 安装器件开发包

4、 安装USB Blaster仿真器驱动

5、 新建工程和工程配置

6、 程序编译和烧写

第3章 实验箱使用注意事项

第4章 逻辑实验

实验1 组合逻辑3-8译码器的设计

实验2 半加器

实验3 全加器

实验4 全减器

实验5 奇偶检验

实验6 编码器

实验7 数据比较器

实验8 多路数据选择器

实验9 二进制码转换成BCD码

实验10 BCD码转换成格雷码

第5章 应用实验

实验1 流水灯实验

实验2 开关量输入输出实验

实验3 数码管显示实验

实验4 4*4矩阵键盘实验

实验5 蜂鸣器演奏实验

实验6 16*16点阵基础实验

实验7 16*16点阵显示汉字实验

实验8 液晶实验

推荐案例

-

TI OMAP-L138 DSP+ARM双核 口袋板DSP+ARM口袋板是广州星嵌电子科技有限公司自主研制而成,由核心板+底板架构组成。选用低功耗TI OMAP-L138处理器(DSP+ARM双内核的架构,定点/浮点 C674x DSP内核 + ARM9内核,主频高达456MHz)。Read More

TI OMAP-L138 DSP+ARM双核 口袋板DSP+ARM口袋板是广州星嵌电子科技有限公司自主研制而成,由核心板+底板架构组成。选用低功耗TI OMAP-L138处理器(DSP+ARM双内核的架构,定点/浮点 C674x DSP内核 + ARM9内核,主频高达456MHz)。Read More -

DSP数字信号处理实验箱 TI C5000 5509TI C5000系列DSP实验箱,TMS320VC5509A架构的定点DSP C55x架构的定点低功专用DSP处理器,主频200MHz。Read More

DSP数字信号处理实验箱 TI C5000 5509TI C5000系列DSP实验箱,TMS320VC5509A架构的定点DSP C55x架构的定点低功专用DSP处理器,主频200MHz。Read More -

C6657+ZYNQ7035/45工业核心板 DSP+FPGA+ARMSOM-XQ6657Z35/45是一款基于TI KeyStone 架构C6000 系列TMS320C6657 双核C66x定点/浮点DSP以及Xilinx Zynq-7000 系列XC7Z035/045 SoC 处理器设计的工业级核心板。Read More

C6657+ZYNQ7035/45工业核心板 DSP+FPGA+ARMSOM-XQ6657Z35/45是一款基于TI KeyStone 架构C6000 系列TMS320C6657 双核C66x定点/浮点DSP以及Xilinx Zynq-7000 系列XC7Z035/045 SoC 处理器设计的工业级核心板。Read More

上一篇

上一篇

已经是最后一篇

已经是最后一篇