ZYNQ(FPGA)与DSP如何实现核间SRIO通讯呢?

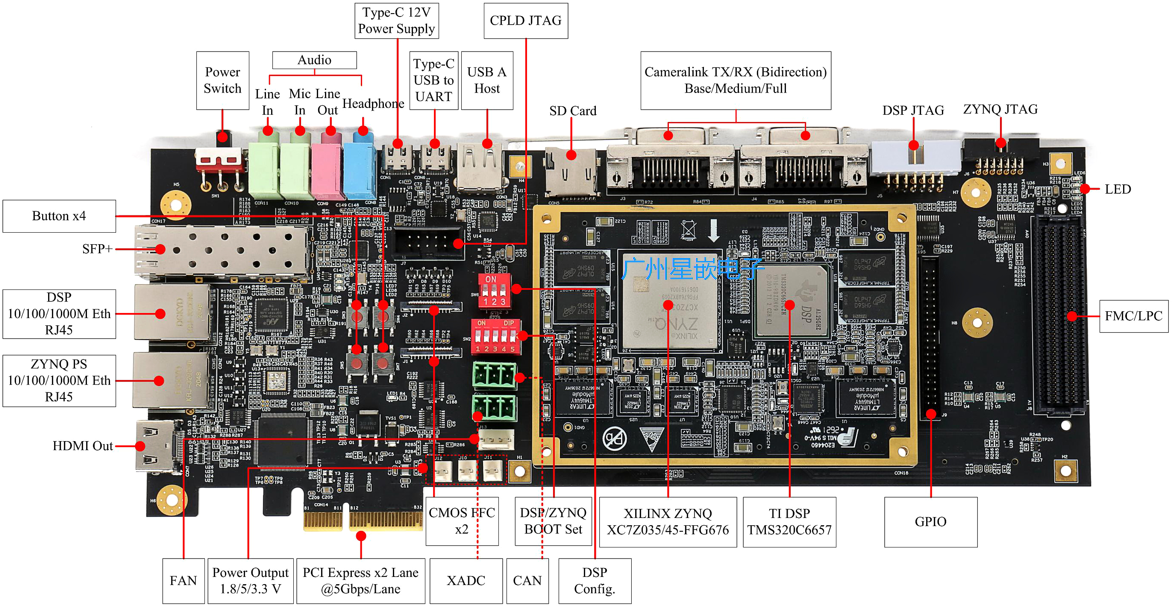

广州星嵌电子科技有限公司(Xines)推出的DSP + ZYNQ评估板XQ6657Z35-EVM,由核心板和底板构成,核心板(SOM-XQ6657Z35)集成了C6657和Zynq-7035/7045两款不同架构的处理器。

那么这款DSP + ZYNQ核心板,是如何实现核间SRIO通讯呢?

1 ZYNQ与DSP之间通信例程

1.1 ZYNQ 与DSP之间SRIO通信

1.1.1 例程位置

ZYNQ例程保存在资料盘中的Demo\ZYNQ\PL\srio_gen2_0_ex文件夹下。

DSP例程保存在资料盘中的Demo\DSP\XQ_SRIO_x4LANE_5Gbps文件夹下。

1.1.2 功能简介

实现DSP与ZYNQ之间SRIO接口传输功能。

DSP与ZYNQ之间SRIO通道宽度为4,每个SRIO通道速率5Gbps。DSP SRIO参考时钟频率为250MHz,ZYNQ SRIO参考时钟频率为125MHz。

DSP与ZYNQ之间SRIO接口相关信号连接示意图如下图所示:

DSP作为Initiator发起NWrite数据写事务,将数据写入ZYNQ PL端的RAM空间(最大2KB);接着,DSP发起NRead数据读事务,从ZYNQ PL端的RAM空间读取数据;DSP完成数据写、读事务后,对读写数据进行比对,以检测SRIO传输是否有数据错误。

1.1.3 例程使用

特别提示:例程使用,请参考下面章节顺序执行。确保ZYNQ PL程序要先运行,然后才能运行DSP程序。

1.1.3.1 加载运行ZYNQ程序

1.1.3.1.1 打开Vivado工程

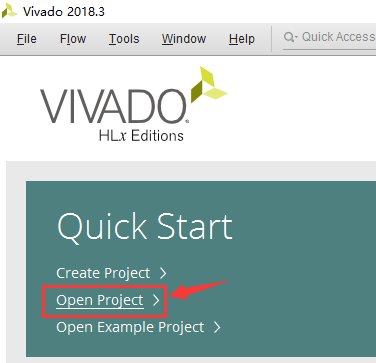

双击桌面Vivado图标,打开Vivado工具:

点击Open Project,打开工程(注意:确保例程路径为非中文路径):

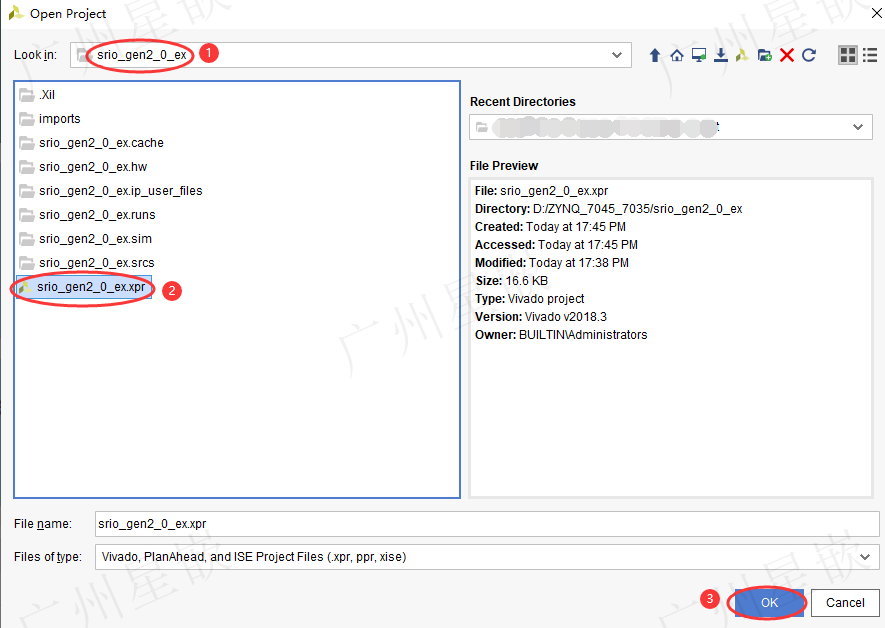

Vivado工程打开后界面如下图所示:

1.1.3.1.2 下载ZYNQ PL程序

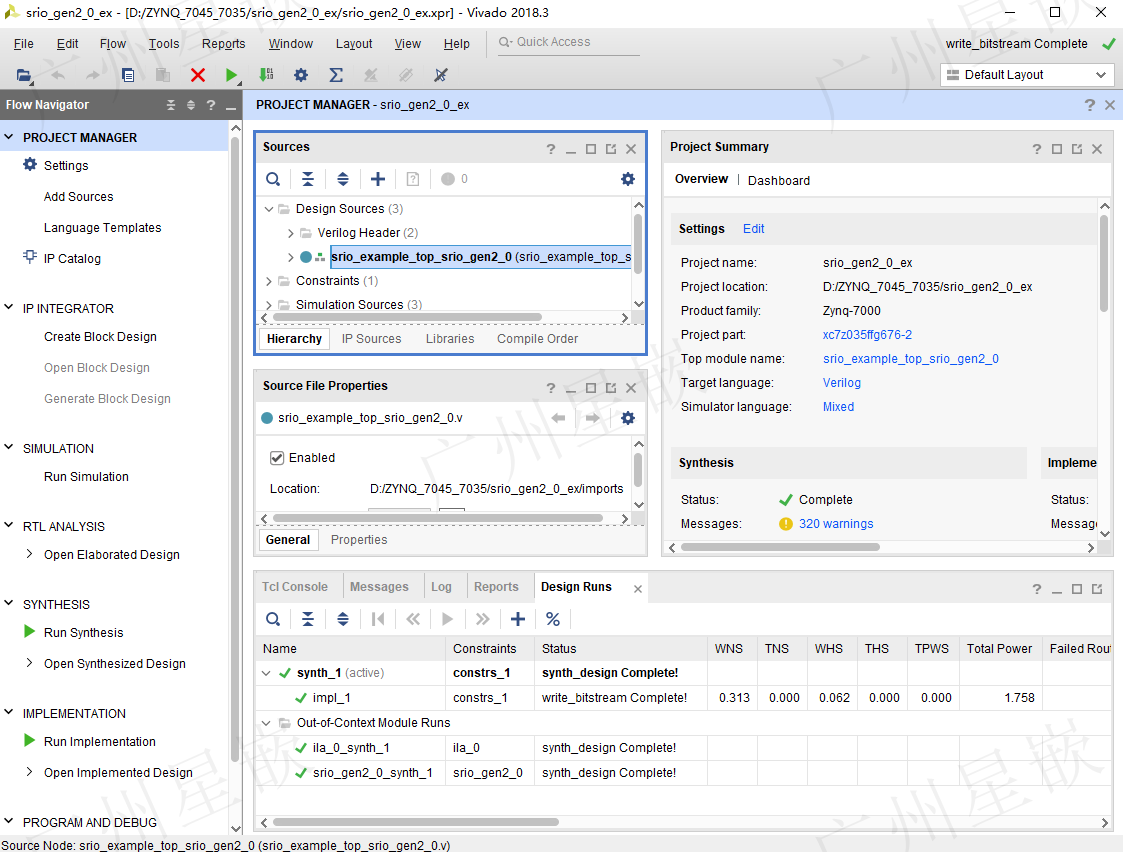

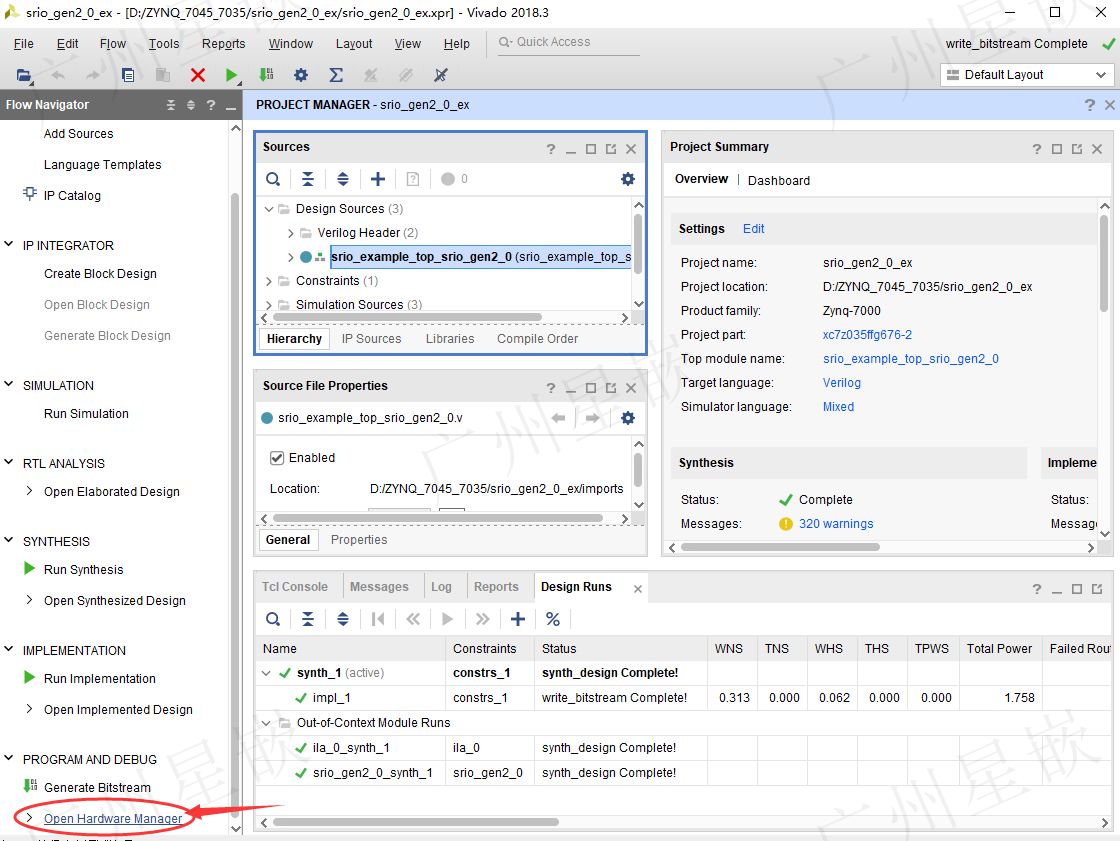

点击Open Hardware Manager:

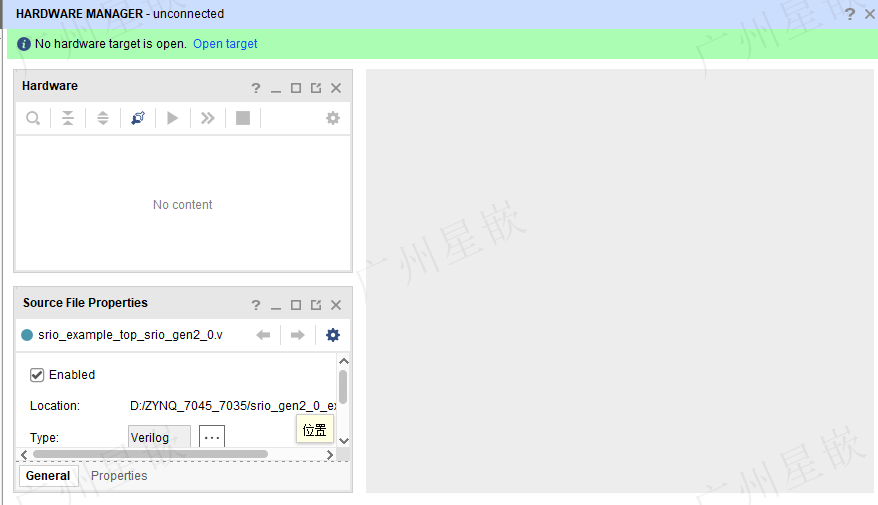

打开Hardware Manager的界面如下图所示:

此后,确保FPGA JTAG仿真器已连至接板卡和电脑,并且板卡处于上电状态。

点击Hardare Manager界面上的Open target,并在弹出的菜单中单击Auto Connect:

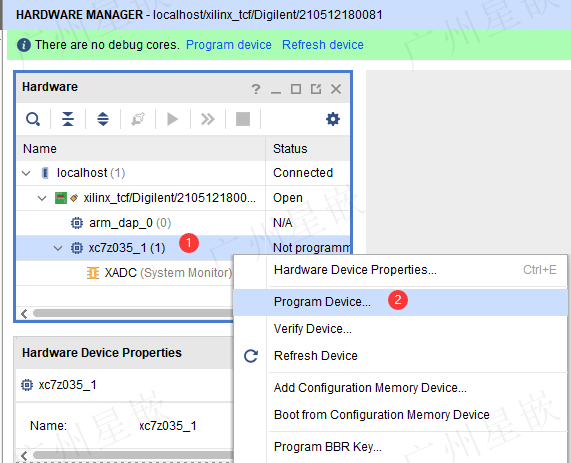

仿真器连接成功后,在找到的xc7z035_1器件上右击,并在弹出的菜单中点击Program Device…:

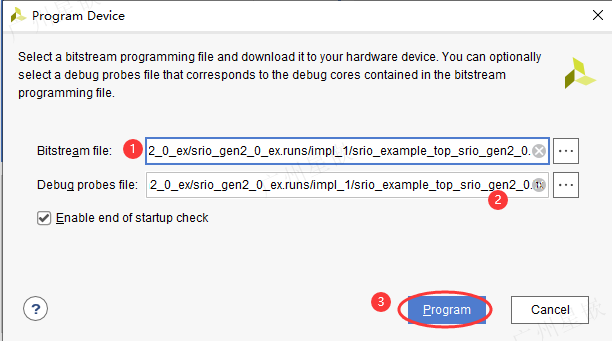

一般来说,Vivado下载工具会自动找到本工程下的程序bit流下载文件和调试文件,如果没有自动找到,则需要用户通过旁边的浏览按钮去自行选取。确保程序下载文件没问题后,点击Program下载程序:

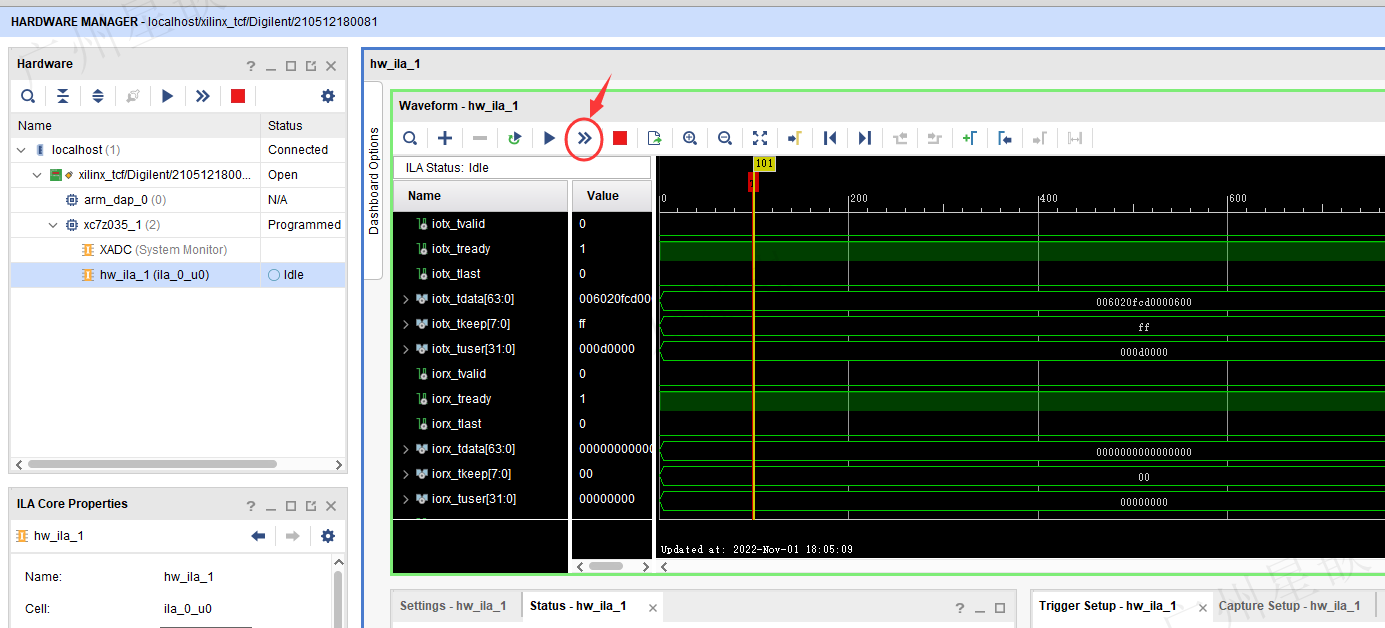

程序下载完成后,点击界面上的“>>”按钮,可实时抓取查看ZYNQ PL端信号运行波形:

1.1.3.2 加载运行DSP程序

1.1.3.2.1 CCS导入例程

双击桌面CCS快捷图标,打开CCS软件:

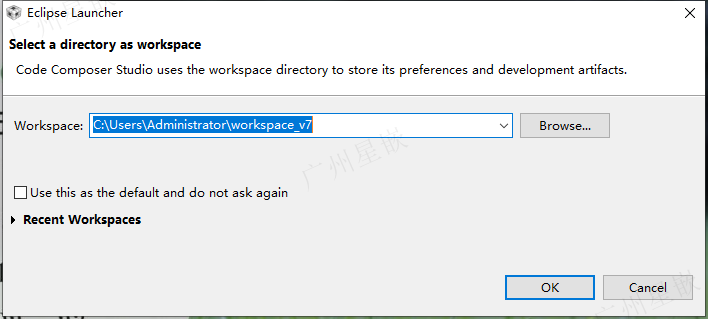

CCS设置工作空间时,选择默认即可:

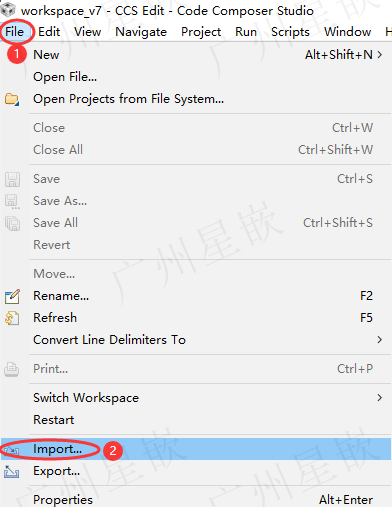

通过菜单File->Import…导入CCS工程:

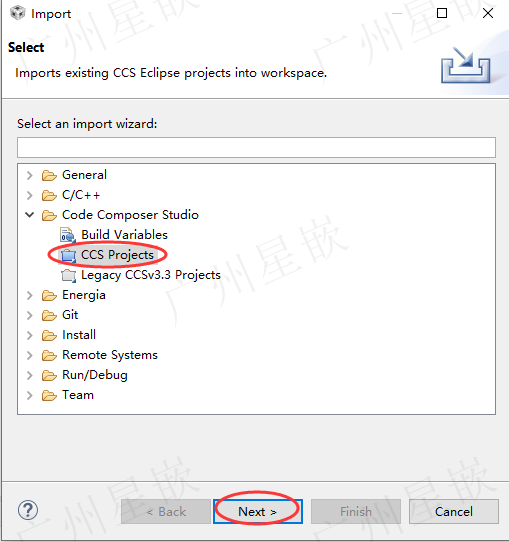

导入项目选择CCS Projects:

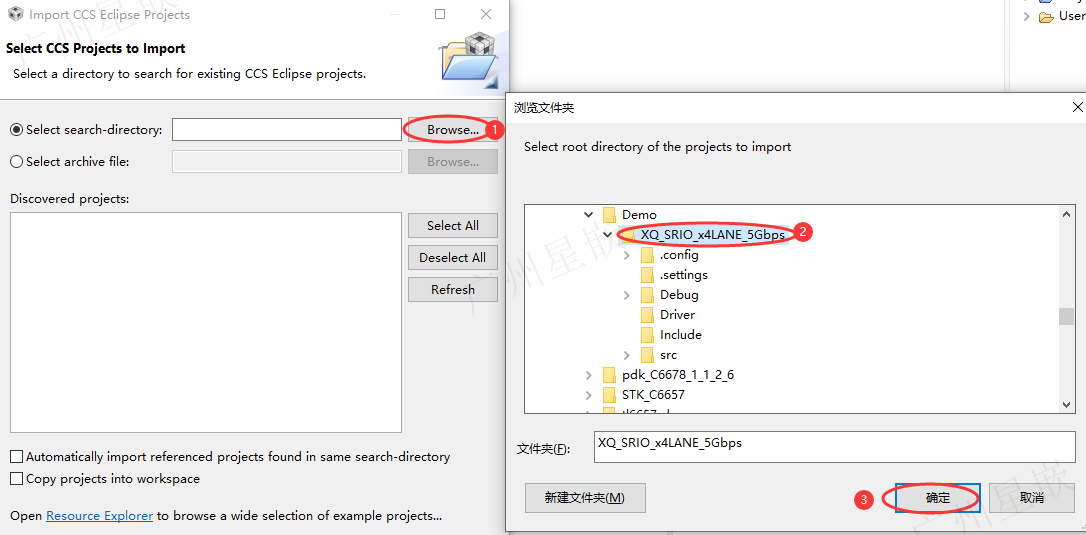

点击Browse…,浏览找到例程所在位置(注意:确保例程路径为非中文路径),选中例程所在目录,并点击“确定”:

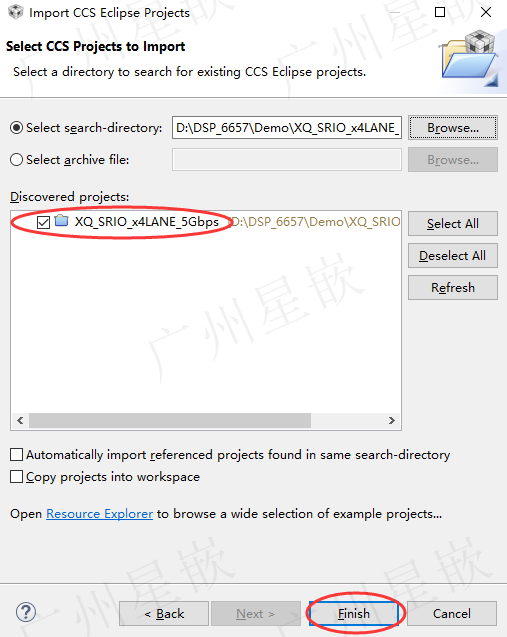

CCS软件将识别到的例程显示在Discovered projects一栏,最后点击Finish:

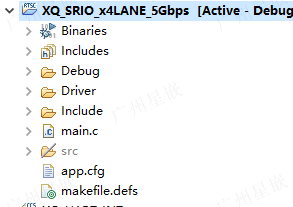

例程导入后界面如下图所示:

1.1.3.2.2 下载CCS程序

1.1.3.2.2.1 目标配置文件设置

特别提示:目标配置文件设置这一步骤可以只进行一次,后面例程可以反复使用,不用重复创建或设置。

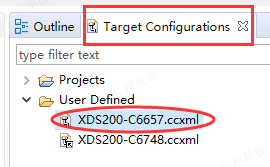

在右边的Target Configuration窗口,双击打开之前创建好的目标配置文件,如下图的XDS200-C6657.ccxml:

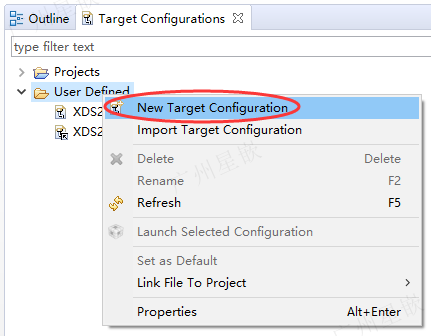

如果还没有目标配置文件,则在Target Configuration窗口的空白处或User Defined文件夹处右击,并在弹出的菜单中点击“New Target Configuration”新建目标配置文件:

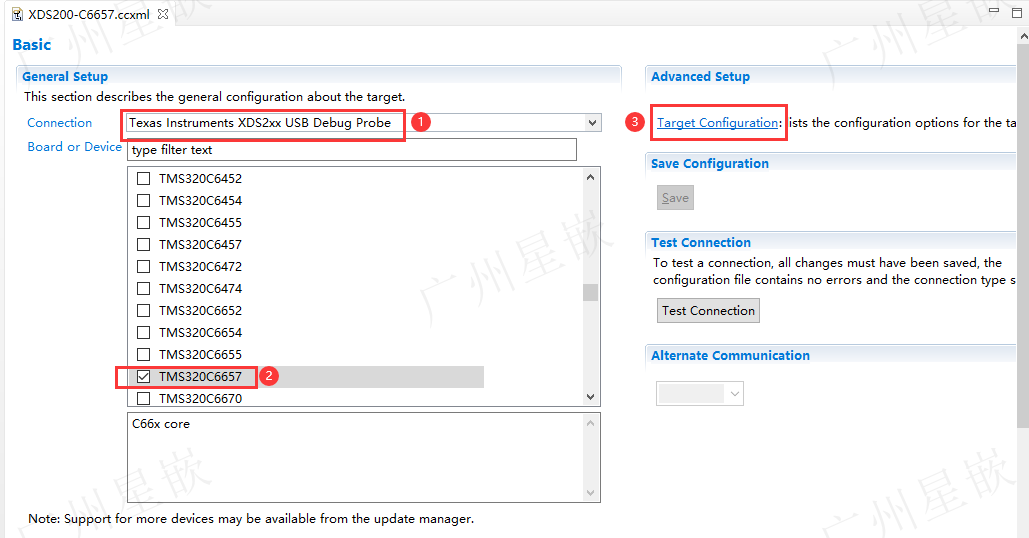

在打开的目标配置文件中,需要配置仿真器类型、器件型号,我们实验用的仿真器为XQ-XDS200U,选中仿真器类型XDS2xx USB Debug Probe即可,器件型号勾选上TMS320C6657,如下图所示,然后点击高级设置项Target Configuration,准备Gel文件设置:

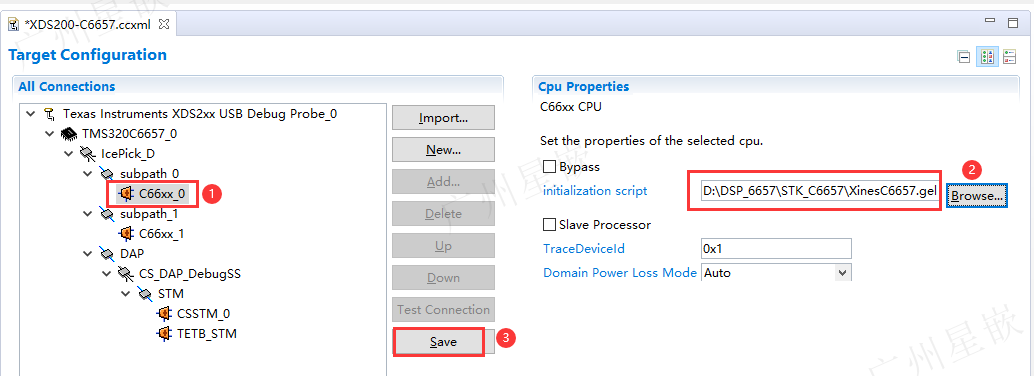

在高级项设置窗口中,点击C66xx_0核心,然后在右侧的初始化脚本栏中,点击Browse,找到我们提供的Gel文件,即XinesC6657.gel。设置完Gel文件后,点击Save:

1.1.3.2.2.2 启动目标配置文件

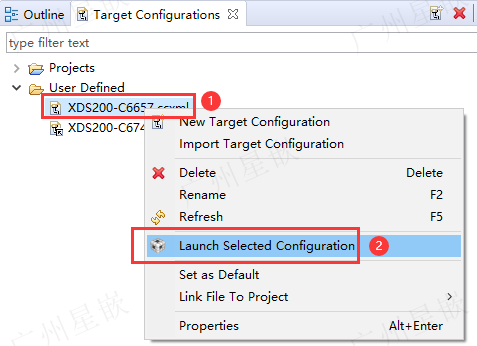

在已经创建并设置好的目标配置文件处右击,并在弹出的菜单中点击Launch Selected Configuration,打开调试窗口:

1.1.3.2.2.3 仿真器连接目标器件

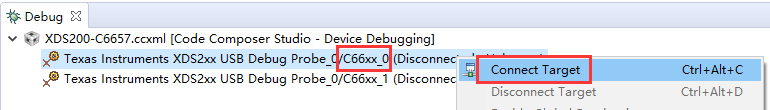

调试窗口打开后,右键单击C66xx_0核心0,并在弹出的菜单中点击Connect Target:

1.1.3.2.2.4 加载DSP程序

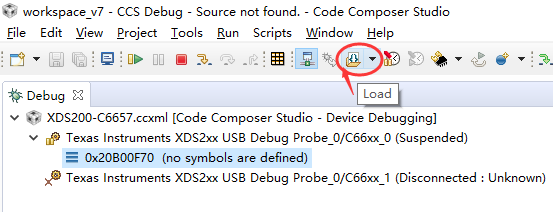

点击Load图标,加载DSP程序:

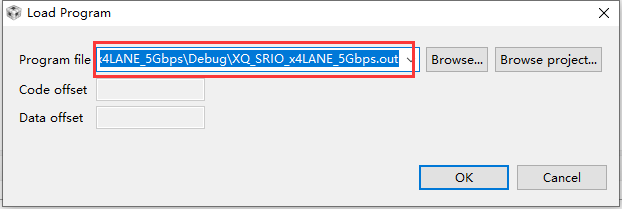

点击Browse…或Browse project…,找到DSP程序的可执行文件(以.out为后缀),然后点击OK,如下图所示:

1.1.3.2.2.5 DSP程序运行

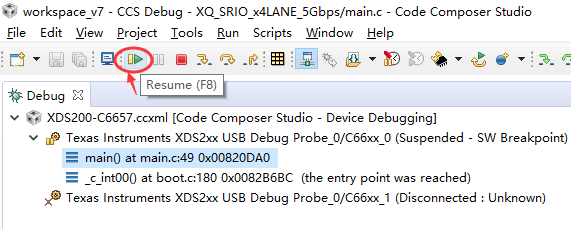

点击Resume运行图标,运行DSP程序,如下图所示:

1.1.3.3 运行结果说明

1.1.3.3.1 DSP程序运行结果

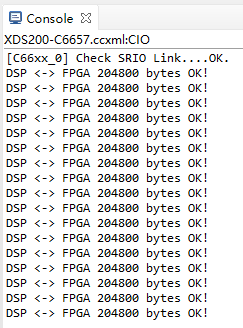

CCS软件的Console控制台窗口打印SRIO调试信息。

DSP通过SRIO接口先发起NWrite写事务,数据长度为2048字节;接着DSP发起NRead事务,数据长度为2048字节,然后比对读写事务对应的数据。

如果SRIO传输异常,存在数据错误,则程序里面错误计数器累加,并输出打印当前错误个数。每当完成100次NWrite和NRead SRIO读写事务,则输出打印一次“DSP <-> FPGA 204800 bytes OK!”字样,如下图所示:

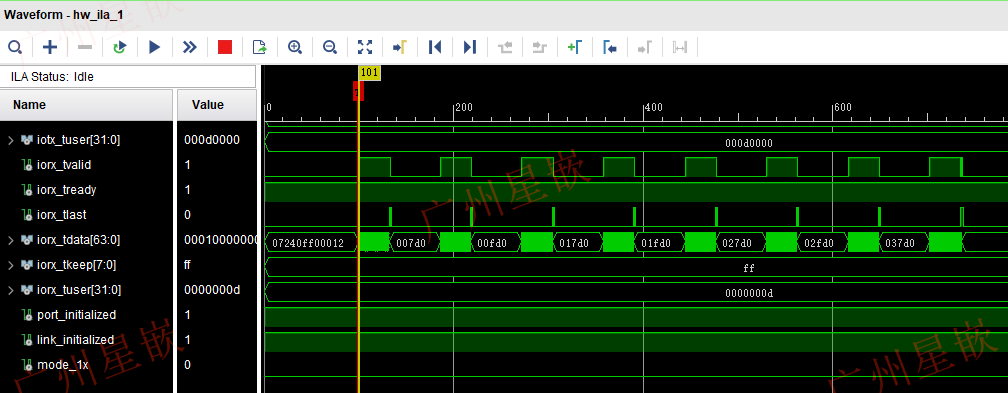

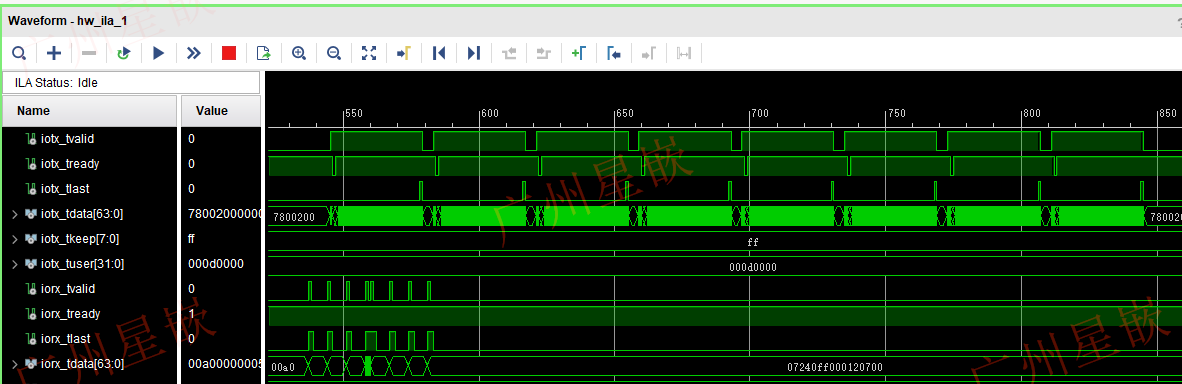

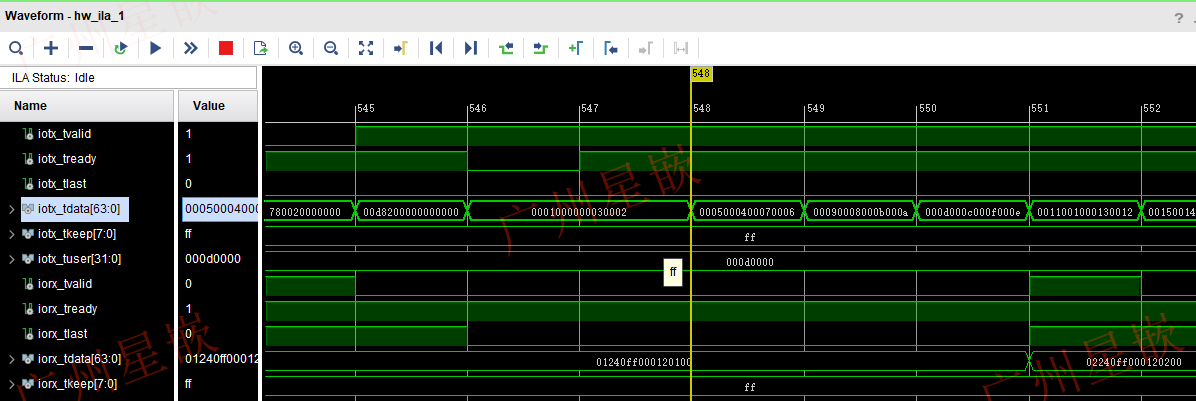

1.1.3.3.2 ZYNQ PL程序运行结果

ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集SRIO本地总线信号时序波形。SRIO本地总线信号说明如下(详细定义请参考数据手册Xilinx文档pg007_srio_gen2.pdf):

SRIO本地发送总线信号 | |

iotx_tvalid | 发送数据有效标志位 |

iotx_tready | 发送准备好标志位 |

iotx_tlast | 最后一个发送数据标志位 |

iotx_tdata | 发送数据 |

iotx_tkeep | 发送数据字节控制位 |

iotx_tuser | 发送控制数据,主要内容是源ID和目的ID |

SRIO本地接收总线信号 | |

iorx_tvalid | 接收数据有效标志位 |

iorx_tready | 接收准备好标志位 |

iorx_tlast | 最后一个接收数据标志位 |

iorx_tdata | 接收数据 |

iorx_tkeep | 接收数据字节控制位 |

iorx_tuser | 接收控制数据,主要内容是源ID和目的ID |

状态信号 | |

port_initialized | SRIO端口初始化完成标志位 1:SRIO端口初始化完成; 0:SRIO端口初始化未完成。 |

link_initialized | SRIO链路初始化完成标志位 1:SRIO链路初始化完成; 0:SRIO链路初始化未完成。 |

mode_1x | SRIO运行模式 1:SRIO运行在降速模式,即4个通道减速到1个通道运行; 0:SRIO运行在全速模式,即4个通道全部运行。 |

ZYNQ端SRIO接收抓取示例如下图所示(对应DSP端发起NWrite事务):

ZYNQ SRIO发送抓取示例如下图所示(对应DSP端发起NRead事务):

1.1.3.4 退出实验

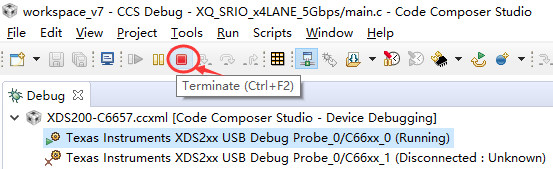

CCS软件窗口上,点击Terminate断开DSP仿真器与板卡的连接:

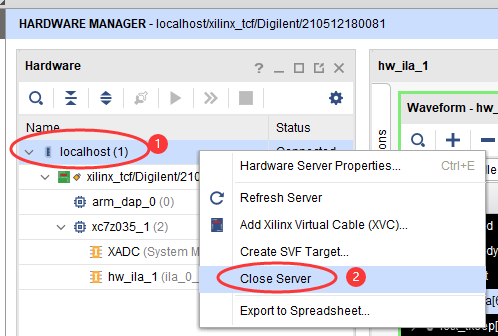

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接:

最后,关闭板卡电源,实验结束。

平台说明:

XQ6657Z35/45-EVM 高速数据处理评估板(XQTyer评估板)由广州星嵌电子科技有限公司自主研发,核心板包含一片TI DSP TMS320C6657和一片Xilinx ZYNQ-7000 SoC 处理器XC7Z035-2FFG676I。

核心板SOM-XQ6657Z35/45引出DSP及ZYNQ 全部资源信号引脚,内部通过SPI、EMIF16、uPP、SRIO通信。

适用于无人机蜂群、软件无线电系统,基带信号处理,无线仿真平台,高速图像采集、处理等领域。

上一篇

上一篇